Многоканальная охранная система

Многоканальная охранная система предназначена для организации охраны нескольких объектов, например дачных участков, или одного объекта, имеющего несколько помещений, нуждающихся в охране. Система подает сигнал по общей для всех датчиков двухпроводной шине и позволяет контролировать исправность датчиков путем световой и (или) звуковой сигнализации.

Система состоит из 12 идентичных блоков кодирования с датчиками тревожного сигнала и пульта декодирования и индикации, соединенных между собой общей двухпроводной линией связи. Работая поочередно, каждый блок кодирования выдает сигнал «Норма». Отсутствие сигнала от какого-либо блока воспринимается, как сигнал «Тревога», т. е. этот сигнал возникает либо при неисправности блока кодирования, либо при срабатывании охранного датчика.

При кодировании и декодировании сигналов используется число импульсный код. Первый датчик выдает в линию пачку из 3 импульсов, второй из 4 импульсов, последний, двенадцатый датчик, выдает 14 импульсов.

Блоки кодирования сделаны так, что они автоматически синхронизируются и выстраиваются в очередь в порядке возрастания числа импульсов в сигнале. Возможна работа системы при использовании от 1 до 12 блоков одновременно.

Система выполнена на КМОП микросхемах серии К176 и К561. Питание блоков кодирования происходит по линии связи.

Технические характеристики:

Число охраняемых объектов......................................................... до 12

Индикация состояния............................................... световая и звуковая

Напряжение питания, В..................................................................... 30

Потребляемый ток:

блок кодирования не более, мА........................................................ 1

блок индикации не более, мА........................................................ 100

Дальность действия, м................................................................. до 300

Размер плат:

блок кодирования, мм............................................................... 65х95

блок индикации, мм.............................................................. 115х 130

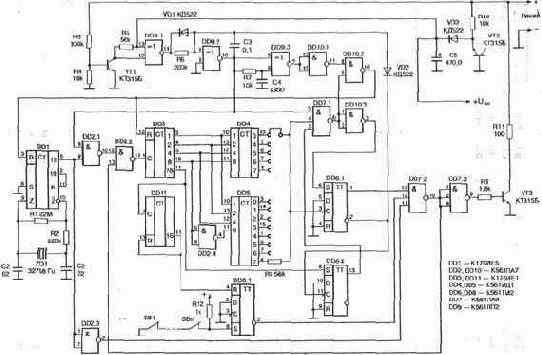

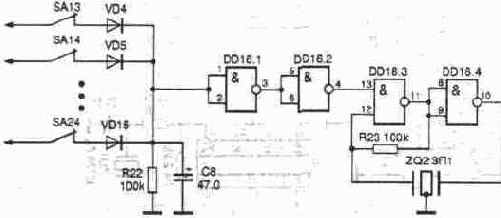

Рассмотрим работу системы, начиная с блока кодирования, принципиальная схема которого представлена на рис. 6. 49.

Все блоки кодирования выполнены по одинаковой схеме, поэтому рассмотрим работу только одного из них — первого. На его вход «Линия» приходят пачки импульсов отрицательной полярности амплитудой 30 В, формируемые поочередно другими блоками. Делитель, выполненный на резисторах R3 и R4, и транзистор VT1 образуют формирователь импульсов амплитудой 7—9 В, необходимых для нормальной работы КМОП микросхем. Элемент DD9. 1 формирует импульсы отрицательной полярности с крутыми фронтом и спадом. Цепь DD9. 2, R6, VD1, СЗ подавляет короткие импульсные помехи и формирует импульс отрицательной полярности, фронт которого совпадает с фронтом первого импульса в пачке на выходе элемента DD9. 1, а спад несколько задержан относительно спада последнего импульса пачки. Элемент DD9. 3, резистор R7 и конденсатор С4 образуют формирователь коротких положительных импульсов по фронту и спаду импульса с выхода элемента DDD9. 2. Эти короткие импульсы, пройдя через элементы DD10. 1, DD10. 2, устанавливают счетчики DD1 и DD3 в нулевое состояние. Счетчик DD3 во время паузы между пачками импульсов считает тактовые импульсы, поступающие на его вход С с тактового генератора через элементы DD2. 1, DD2. 2. Генератор тактовых импульсов выполнен на микросхеме DD1, частота которого стабилизирована кварцевым резонатором ZQ1. С вывода 11 микросхемы DD1 импульсы с частотой 32768 Гц поступают на вход делителя частоты на 64 (вывод 2). После деления импульсы с частотой 512 Гц с вывода 5 поступают на счетчик DD3 для определения длительности паузы между пачками импульсов.

Рис. 6. 49. Принципиальная схема блока кодирования

Применение кварцевого генератора обеспечивает высокую стабильность работы системы и исключает необходимость дополнительной подстройки всех генераторов. Работа тактового генератора и счетчика DD3 синхронизированы с началом и концом пачки импульсов, поступающих на их входы R. Счетчик DD3 во время паузы между пачками считает тактовые импульсы, следующие с частотой 512 Гц (вывод 5 микросхемы DD1), измеряя таким образом длительность паузы между пачками.

Если длительность паузы превышает 16 периодов тактовых импульсов, сигналом с выхода 16 (вывод 11) микросхемы DD3 D-триггер DD6. 2 устанавливается в единичное состояние (это происходит одновременно во всех блоках кодирования), после чего продолжается измерение паузы. И если перемычка в блоке кодирования соединяет вывод 15 микросхемы DD4 и вывод 4 элемента DD7. 1, то спустя три импульса после переключения триггера DD6. 2 сигнал логической единицы с выхода 3 дешифратора DD4 (вывод 15) переключает элемент DD7. 1, логический нуль с его выхода через элемент DD10. 2 устанавливает счетчики DD1 и DD3 в нулевое состояние, а триггер DD6. 1 — в единичное. Уровень логической единицы с прямого выхода триггера DD6. 1 разрешает прохождение тактовых импульсов через элементы DD7. 2 и DD7. 3 на базу транзистора VT3. При этом на его коллекторе формируется пачка из трех импульсов отрицательной полярности.

Нагрузкой транзистора VT3 служит резистор, находящийся в блоке индикации (R9). Счетчик DD3 считает импульсы в пачке, приходящие на его вход С (вывод 1) через элемент DD2. 2. По окончании третьего импульса на выходе 3 дешифратора DD4 (вывод 15) появляется логическая единица. Этот сигнал не включает элемент DD7. 1, т. к. на выходе элемента DD9. 2 присутствует логический нуль, но устанавливает триггер DD6. 1 в нулевое состояние, что, в свою очередь, переводит триггер DD6. 2 также в нулевое состояние. В результате блок кодирования прекращает выдачу импульсов до появления паузы длительностью 16 импульсов, которая во всех блоках кодирования переключает триггеры DD6. 2 в единичное состояние и активизирует их работу.

В том случае, если во втором блоке кодирования перемычка подключена в выводу 1 (выход 4) дешифратора DD4, то после паузы в четыре импульса этот блок выдает пачку из четырех импульсов и также прекратит работу до появления паузы длительностью 16 импульсов. Следующим сработает блок, в котором перемычка подключена к выходу 5 дешифратора DD4 (вывод 6), и выдаст 5 импульсов и т. д.

После срабатывания последнего из подключенных к системе блоков триггеры DD6. 1 всех блоков устройства запретят выдачу импульсов. Возникнет пауза длительностью 16 импульсов, активизирующая работу всех блоков. Далее цикл работы системы повторится.

Длительность полного цикла работы всех блоков кодирования при частоте тактовых импульсов 512 Гц составляет около 0, 5 с.

В зависимости от установленной перемычки блок кодирования выдает от 3 до 14 импульсов в пачке. На случай нарушения контакта введен резистор R8, обеспечивающий выдачу пачки из 15 импульсов.

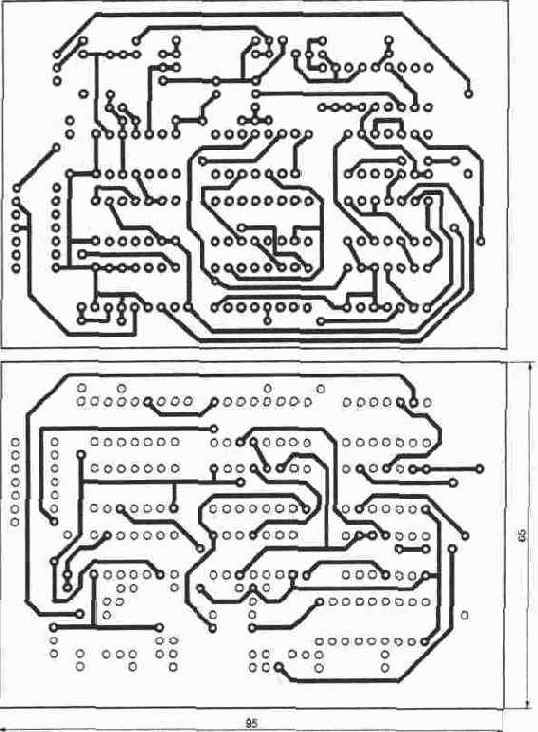

Рис. 6. 50. Печатная плата блока кодирования

При срабатывании одного из охранных датчиков (SB1 —SBn) триггер DD8. 1 переключается, в единичное состояние, на его инверсном выходе (вывод 2) появляется уровень логического нуля, закрывающий элемент DD7. 2 и прекращающий выдачу импульсов в линию этим блоком. После восстановления контактов кнопок SB1 —SBn триггер DD8. 1 устанавливается в исходное состояние импульсом с вывода 11 счетчика DD11.

Питание блока кодирования осуществляется по линии связи от источника + 30 В. Транзистор VT2 выполняет функцию стабилитрона. Диод VD3 предотвращает разряд конденсатора С5 при прохождении пачек импульсов.

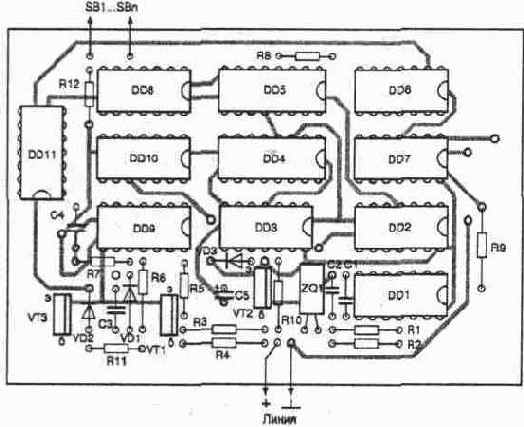

Рис. 6. 51. Размещение деталей на плате блока кодирования

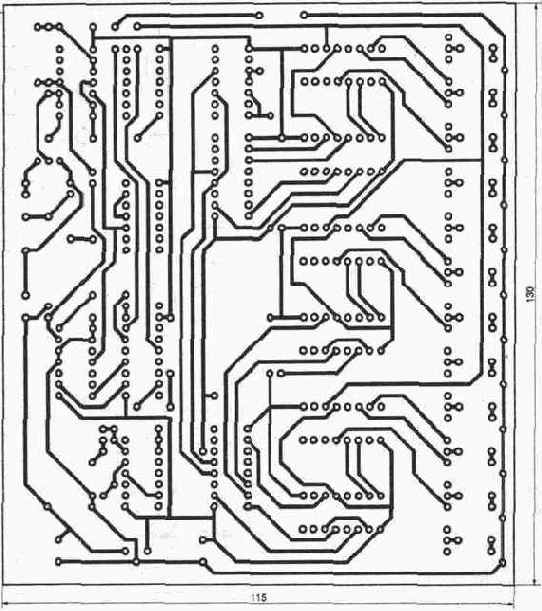

Каждый из блоков кодирования выполнен на отдельной печатной плате размером 65х95 мм. Плата изготовлена из двухстороннего стеклотекстолита, ее внешний вид представлен на рис. 6. 50.

В блоке используются микросхемы серий К176, К561. Кварцевый рехонетор ZQ1 — часовой, с частотой резонанса 32768 Гц. Перемычка, определяющая номер блока и, соответственно, число импульсов в пачке, выполняется тонким монтажным проводом. Размещение деталей на плате блока кодирования представлено на рис. 6. 51.

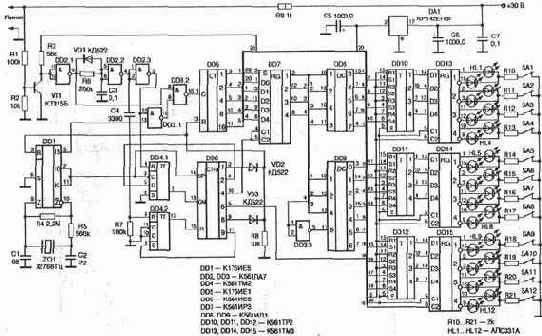

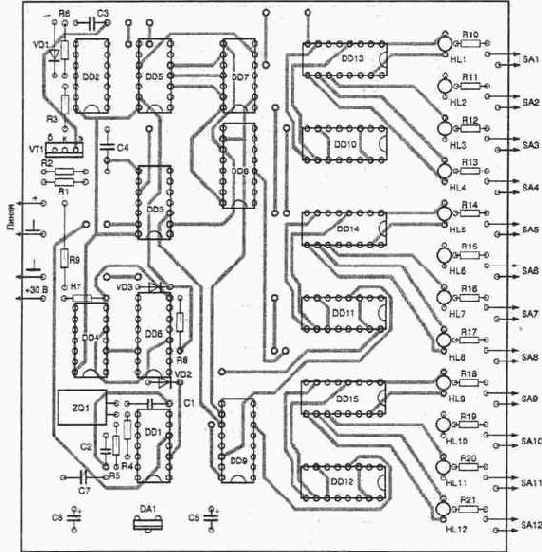

Блок индикации выполнен в виде отдельной платы и размещается в одном корпусе с источником питания. Принципиальная схема блока индикации представлена на рис. 6. 52. Блок питания может использоваться любой на постоянное напряжение 30 В и ток не менее 0, 3 А. Питание блоков кодирования осуществляется по линии связи постоянном напряжением 30 В, а блока индикации — от стабилизатора, выполненного на специализированной микросхеме DA1 КР142ЕН8Г.

Импульсы, поступающие с линии, через делитель напряжения на резисторах Rl, R2 поступают на базу транзистора VT1, который совместно с элементом DD2. 1 образует формирователь импульсов с крутыми фронтами и спадами, тем самым повышая помехоустойчивость всей системы в целом. Элементы DD2. 2 и DD2. 3, а также R6, VD1, СЗ формируют импульс, фронт которого совпадает с фронтом первого импульса в пачке, а спад несколько задержан относительно спада последнего импульса в пачке. Нулевой уровень с выхода 3 элемента DD2. 3 закрывает элемент DD3. 1 и разрешает прохождение импульсов пачки на вход С (выход 1) счетчика DD5 через элемент DD3. 2.

Рис. 6. 52. Принципиальная схема блока индикации

На триггерах DD4. 1, DD4. 2 и счетчике DD6 выполнено устройство, формирующее импульсы записи и обнуления счетчиков DD1 и DD5. В исходном состоянии на вход С триггера DD4. 1 и вход СР счетчика DD6 поступают импульсы с тактового генератора (вывод 11 микросхемы DD1) частотой 32768 Гц. Однако счетчик DD6 эти импульсы не считает, т.к: на его входе R присутствует высокий логический уровень, поступающий с прямого выхода (выход 13) триггера DD4. 2. По фронту первого импульса пачки положительный перепад с вывода 4 элемента DD2. 2, продифференцированный цепью C4R7, устанавливает триггер DD4. 2 в нулевое состояние. Счетчик DD6 начинает считать тактовые импульсы. Положительный импульс с вывода 2 счетчика DD6 через диод VD2 устанавливает счетчики DD1 и DD5 в нулевое состояние, синхронизируя их работу. С приходом еще двух импульсов на счетчик DD6 единичный уровень появляется на выводе 4 счетчика и входе D триггера DD4. 1, при этом на выходе последнего появляется единичный уровень, запрещающий по входу CN счет импульсов со входа СР счетчика DD6. По окончании пачки импульсов положительным перепадом на входе R триггер DD4. 1 устанавливается в нулевое состояние. Счетчик DD6 вновь начинает считать тактовые импульсы. На его выходах появляются положительные импульсы. Первый из них (с вывода 10) производит запись информации в регистр DD7. На выходах последнего появляется код числа, соответствующего количеству импульсов в пачке. Этот код преобразуется дешифраторами DD8, DD9 в единичный уровень на одном из выходов, соединенных с соответствующим входом S триггеров DD10, DD11, DD12 соответственно. Уровень логической единицы фиксируется на соответствующем выходе этих триггеров.

Следующим положительным импульсом с выхода 6 счетчика DD6 (вывод 5) производится запись информации в D-триггеры DD13, DD14, DD15. Положительное напряжение, появляющееся на прямом выходе этих триггеров вызовет включение одного из светодиодов зеленого свечения (например, HL1), входящего в состав двухцветного светодиода типа АЛС331А. При отсутствии сигналов с блоков кодирования, соответствующие светодиоды загораются красным цветом. Для удобства пользования индикацию неиспользуемых каналов можно отключить переключателями SA1—SA12.

Рис. 6. 53. Принципиальная электрическая схема блока звуковой индикации

Рис. 6. 54. Печатная плата блока индикации

Очередным импульсом со счетчика DD6 (вывод 9) счетчики DD1 и DD5 устанавливаются (через диод VD3) в исходное состояние. А сам счетчик DD6 устанавливается в нулевое состояние, т. к. импульс с вывода 11 устанавливает триггер DD4. 2 в единичное состояние, в котором он будет находиться до прихода очередной пачки импульсов.

При отсутствии импульсов на входе блока счетчик DD5 считает тактовые импульсы частотой 512 Гц, поступающие с вывода 5 счетчика DD1 через элементы DD3. 1, DD3. 2. Во время паузы длительностью 16 тактов на выходе 16 (вывод 11) счетчика DD5 появится логическая единица и произойдет обнуление триггеров DD10, DD11, DD12. Устройство готово к приему нового пакета данных.

Рис. 6. 53. Размещение деталей на плате блока индикации

При необходимости блок индикации можно дополнить звуковой индикацией. Принципиальная схема блока звуковой индикации приведена на рис. 6. 53.

Блок состоит из задающего генератора звуковой частоты и схемы управления. Он подключается к инверсным выходам триггеров DD13, DD14, DD15. Когда на этих выходах появляется уровень логической единицы, индицирующий сигнал тревоги, загорается красный светодиод, через один из диодов VD4 —VD 15 быстро заряжается конденсатор С8 и уровень единицы с вывода 4 элемента DD16. 2 разрешает работу звукового генератора. При пропадании сигнала тревоги генератор работает еще некоторое время, до момента разряда конденсатора С8 через резистор R22. Переключатели SA13—SA24 служат для выборочного отключения звуковой индикации некоторых каналов. При желании возможно использовать сдвоенные переключатели (SA1 и SA13, SA2 и SA14 и т. д.) для одновременного отключения световой и звуковой индикации соответствующих каналов.

Блок индикации выполнен на микросхемах серий К176 и К561 и смонтирован на печатной плате из двухстороннего фольгированного стеклотекстолита размером 115х130 мм (рис. 6. 54).

Размещение деталей, включая светодиоды, показано на рис. 6. 55.

Устройство не вызывает особых трудностей в настройке, и если собрано из заведомо исправных деталей, сразу готово к использованию.

В качестве линии связи можно использовать обычную двухпроводную линию, провода которой желательно свить в жгут для уменьшения наводок и помех, или использовать экранированный провод.

Линия связи может быть и беспроводной. При этом можно воспользоваться ИК или радиоканалом. Рассмотрим подробнее организацию линии связи по радиоканалу, как наиболее предпочтительную. Для этого необходимо дополнить каждый блок кодирования передатчиком и радиоприемником, а блок индикации — только радиоприемником. Все передатчики могут работать на одной частоте. Питание блоков в этом случае должно осуществляться от автономного источника питания.

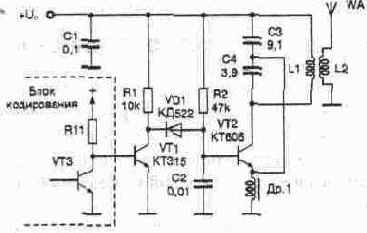

Принципиальная схема простейшего передатчика для блоков кодирования приведена на рис. 6. 56.

Передатчик работает на частоте 85 МГц. Модуляция осуществляется путем срыва ВЧ колебаний генератора, выполненного на транзисторе VT2 типа КТ606. Модулирующий сигнал снимается с коллектора транзистора VT3 блока кодирования (рис. 6. 49) и периодически закрывает транзистор VT1. При этом диод VD1 закрывается положительным напряжением, генератор возбуждается, излучая сигнал данного блока. При открывании транзистора VT1 база транзистора VT2 через диод VD1 замыкается на общий провод, генерация срывается. Таким образом осуществляется смешанная амплитудно-частотная модуляция. В данном случае прием сигнала возможен как на ЧМ, так и на AM приемник.

Транзистор VT2 можно заменить на КТ904 или КТ907. Дроссель Др1 намотан на корпусе резистора МЛТ-0, 5 сопротивлением более 100 кОм проводом

Рис. 6. 56. Схема передатчика блока кодирования

Рис. 6. 57. Приемное устройство блока кодирования

ПЭВ-1 0, 16 мм и имеет 60 витков. Катушки L1 и L2 бескаркасные диаметром 3 мм. Катушка L1 имеет 5 витков, катушка L2 — 1 виток, намотанный поверх катушки L1 проводом ПЭВ-1 0, 35 мм.

Настройка передатчика особенностей не имеет.

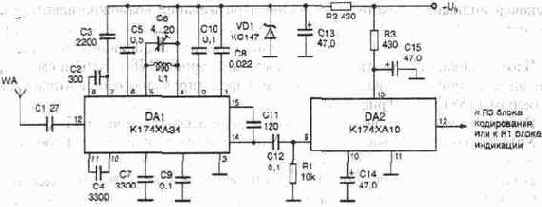

Приемник можно выполнить, например, по схеме, приведенной на рис. 6. 57.

Приемное устройство выполнено на двух специализированных микросхемах К174ХА34 и К174ХА10. Радиотракт выполнен на микросхеме DA1. Она содержит полный супергетеродинный тракт ЧМ приемника, и на ее выходе (вывод 14) формируется низкочастотный сигнал. Кроме того, микросхема содержит встроенную схему бесшумной настройки, что в данном случае очень важно, т. к. необходимо, чтобы в режиме ожидания приемник не воспринимал помехи. Частота настройки определяется контуром L1C6 гетеродина.

Усилитель 34 собран на микросхеме DA2, с выхода которой (вывод 12) сигнал поступает на резисторы R3 или R1 блоков кодирования или блока индикации соответственно. При этом номиналы резисторов уменьшают и подбирают при настройке по наиболее надежному срабатыванию устройства.

Катушка L1 диаметром 3 мм намотана проводом ПЭВ-1 0, 35 мм и содержит 5 витков.

В устройстве можно использовать приемники и передатчики с кварцевой стабилизацией частоты, что позволит повысить надежность системы в целом.